Página 1 de 1

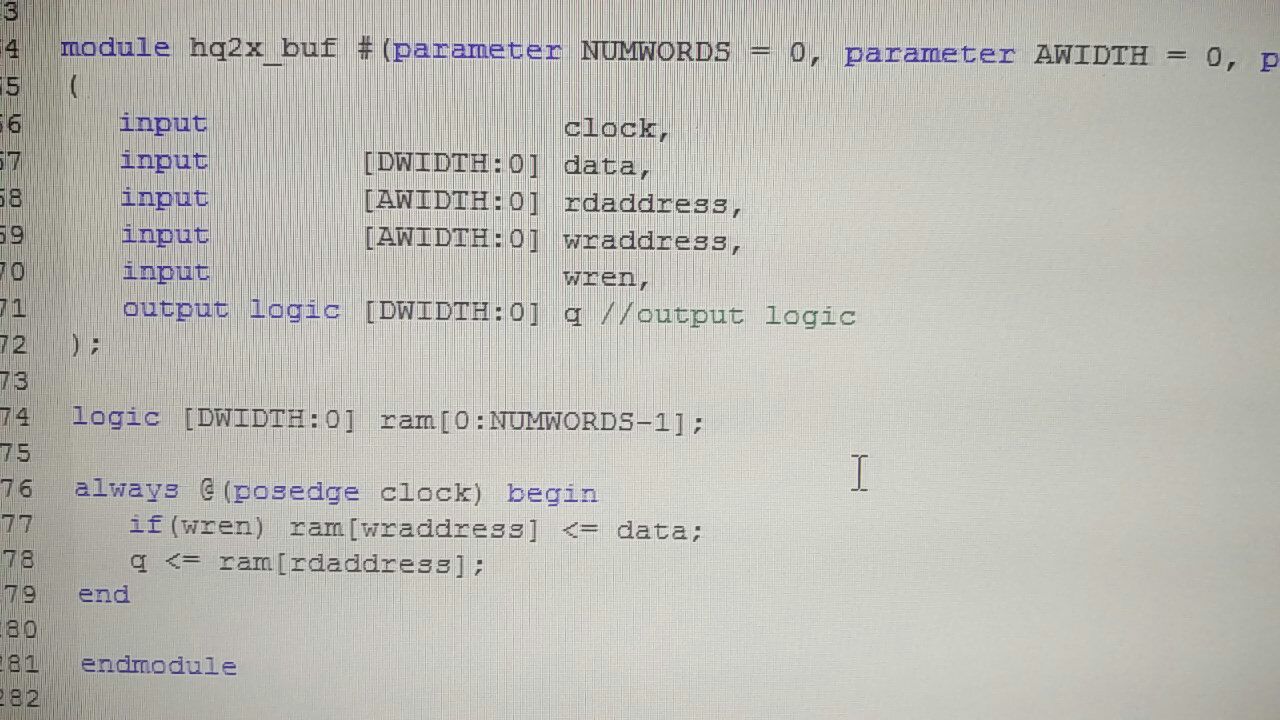

¿A qué se traduce "output logic" en este código?

Publicado: 20 Ago 2018, 14:43

por mcleod_ideafix

Pregunta de Neuro_999 en el Telegram:

Como puedo poner eso en verilog? Q me casca y estaba con el de nes para ponerlo en rgb vga

El output logic ese no lo traga

- outputlogic.jpg (160.7 KiB) Visto 7238 veces

Respuesta rápida: es un

output reg

Respuesta menos rápida: fíjate que q, que es la salida que te interesa, es asignada mediante una asignación no bloqueante ( <= ) dentro de un always con un reloj (o sea, un always secuencial). Dentro de un always secuencial, todos los destinos de asignaciones deben ser "reg" en Verilog, así que q debe ser un reg, en este caso, un output reg.

En SystemVerilog, para acabar con la confusión (la hay? yo no me confundo, la verdad) entre wire y reg, o entre reg combinacional y reg secuencial, crearon el "logic" (que realmente no sé si contribuye más a la confusión o no...)

Re: ¿A qué se traduce "output logic" en este código?

Publicado: 20 Ago 2018, 14:45

por neuro_999

Muchas gracias.

La verdad es q el .sv es un poco cristo cuando lo que mas gas usado es vhdl y un poco de verilog

Re: ¿A qué se traduce "output logic" en este código?

Publicado: 20 Ago 2018, 14:46

por mcleod_ideafix

Neuro, lo que estás definiendo ahí es una memoria de doble puerto, con un puerto de escritura y otro de lectura. Cuando pases el sintetizador, sería conveniente que "ram" es realmente detectada como una memoria de tipo Block RAM con dos puertos. Como no lo haga y te lo sintetice con LUTs, puedes perder mucho espacio de la FPGA (y tiempo de síntesis) si NUMWORDS es un valor alto.

Re: ¿A qué se traduce "output logic" en este código?

Publicado: 20 Ago 2018, 15:43

por wilco2009

mcleod_ideafix escribió: ↑20 Ago 2018, 14:43

En SystemVerilog, para acabar con la confusión (la hay? yo no me confundo, la verdad) entre wire y reg, o entre reg combinacional y reg secuencial, crearon el "logic" (que realmente no sé si contribuye más a la confusión o no...)

Pero entonces no me acaba de quedar claro qué es el "output logic" en System Verilog. ¿permite al sintetizador que elija si es un reg o un wire dependiendo del contexto?

Re: ¿A qué se traduce "output logic" en este código?

Publicado: 20 Ago 2018, 16:38

por mcleod_ideafix

wilco2009 escribió: ↑20 Ago 2018, 15:43

mcleod_ideafix escribió: ↑20 Ago 2018, 14:43

En SystemVerilog, para acabar con la confusión (la hay? yo no me confundo, la verdad) entre wire y reg, o entre reg combinacional y reg secuencial, crearon el "logic" (que realmente no sé si contribuye más a la confusión o no...)

Pero entonces no me acaba de quedar claro qué es el "output logic" en System Verilog. ¿permite al sintetizador que elija si es un reg o un wire dependiendo del contexto?

Pues no estoy muy seguro, pero por lo visto la cosa es que en Verilog "reg" se puede usar tanto para denotar una señal como para un flipflop. Todo depende de en qué tipo de "always" se encuentre. "logic" por otra parte, siempre denota un flipflop y nunca una señal (un cable, vamos).

Voy a ver si lo miro y te confirmo si es eso o no.

EDITO:

Pues va a ser que no es exactamente como lo dije, sino que parece que "logic" se usa exactamente igual que "reg", que son sinónimos.

https://electronics.stackexchange.com/q ... explainati